19/04/2025

En el fascinante universo del diseño de hardware digital, VHDL (VHSIC Hardware Description Language) se erige como una herramienta indispensable. Pero, ¿qué es lo que realmente potencia este lenguaje y permite a los ingenieros modelar sistemas complejos con precisión? La respuesta reside, en gran medida, en sus bibliotecas estándar. Estas colecciones predefinidas de tipos de datos, funciones y procedimientos son el andamiaje sobre el cual se construyen los diseños más sofisticados, asegurando coherencia, eficiencia y, crucialmente, la capacidad de simular el comportamiento de circuitos antes de su implementación física.

Comprender las bibliotecas estándar de VHDL no es solo una cuestión de sintaxis, sino de entender la filosofía detrás del diseño de hardware. Nos permiten abstraernos de los detalles más básicos para centrarnos en la lógica del sistema, a la vez que proporcionan herramientas para interactuar con el entorno de simulación y garantizar que nuestros diseños se comporten como se espera. Sin ellas, cada diseñador tendría que reinventar la rueda constantemente, un escenario impensable en un campo tan dinámico y exigente.

La Biblioteca 'std': El Fundamento del Lenguaje

La biblioteca std, o "estándar", es la base sobre la que se asienta cualquier diseño VHDL. Es intrínseca al lenguaje y, en muchos entornos de desarrollo, se carga de forma implícita. Dentro de esta biblioteca, encontramos dos paquetes fundamentales que todo diseñador debe conocer:

Paquete standard: El Corazón de los Tipos de Datos y Operaciones

El paquete standard es, como su nombre indica, el paquete estándar por excelencia. Contiene las definiciones de los tipos de datos fundamentales que utilizamos en VHDL para describir señales, variables y constantes. Tipos como BIT (que puede ser '0' o '1'), BOOLEAN (TRUE o FALSE), INTEGER (números enteros dentro de un rango definido por la implementación), REAL (números de punto flotante), TIME (para modelar retardos y tiempos en la simulación), y CHARACTER son solo algunos ejemplos de lo que este paquete provee. Además de los tipos, standard define una serie de operaciones lógicas y aritméticas básicas que pueden aplicarse a estos tipos, permitiendo la construcción de expresiones complejas que describen el comportamiento del hardware.

La existencia de estos tipos y operaciones predefinidas simplifica enormemente el proceso de codificación, ya que el diseñador no tiene que preocuparse por cómo representar un número entero o cómo realizar una operación AND; el lenguaje ya lo proporciona de manera eficiente y estandarizada.

Paquete textio: Interacción con el Mundo Exterior

El paquete textio es una herramienta poderosa, especialmente invaluable en el contexto de la verificación y la simulación. Su propósito principal es definir el manejo de textos y archivos. Esto significa que permite a los diseñadores VHDL leer y escribir datos desde y hacia archivos de texto externos al entorno de simulación. ¿Por qué es esto tan importante? Imagina que necesitas probar un diseño con miles de combinaciones de entradas, o que deseas registrar los resultados de una simulación para un análisis posterior.

Con textio, puedes:

- Leer vectores de prueba (estímulos) desde un archivo para alimentar tu diseño durante la simulación, automatizando el proceso y haciéndolo repetible.

- Escribir los resultados de la simulación (salidas, estados internos) a un archivo, lo que facilita el análisis de datos, la depuración y la generación de informes detallados.

- Crear mensajes informativos o de depuración en la consola de simulación, ayudando a entender el flujo de ejecución del diseño.

Esta capacidad de interactuar con archivos externos transforma la simulación de un proceso manual en una metodología robusta y automatizada, esencial para la validación de diseños complejos.

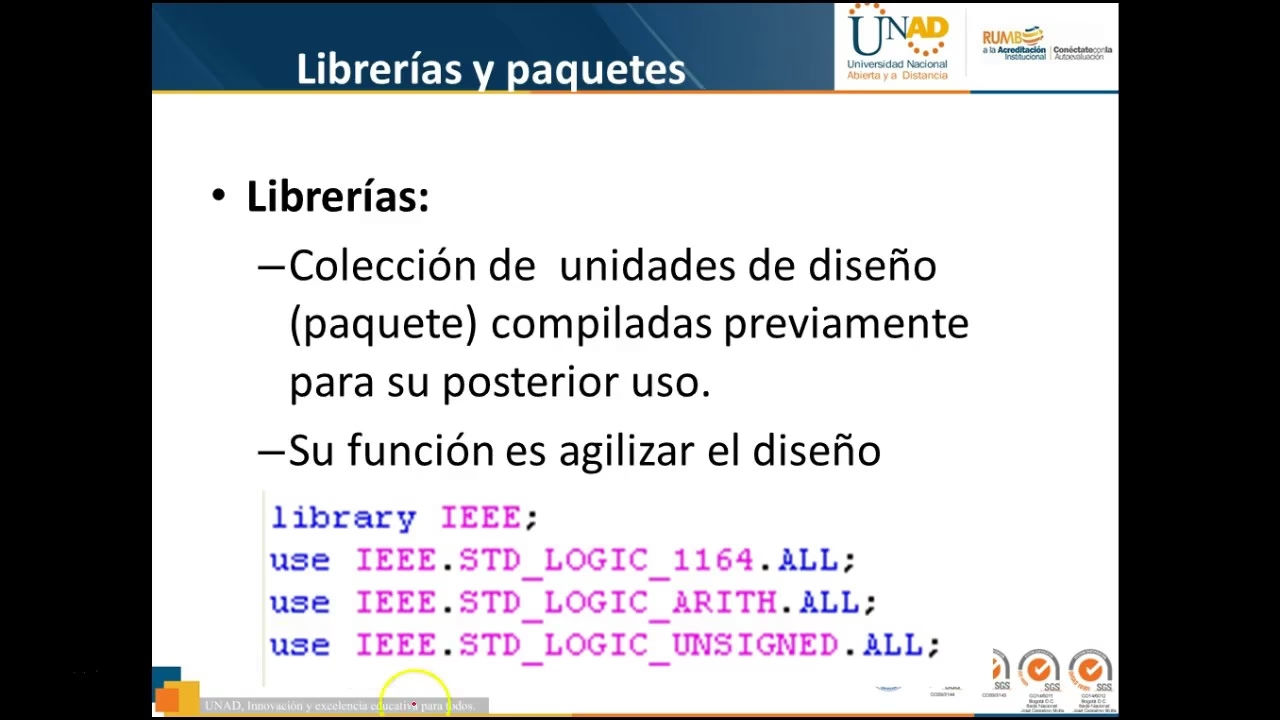

La Biblioteca 'ieee': Estandarización y Robustez

Mientras que la biblioteca std proporciona los fundamentos del lenguaje, la biblioteca ieee (Instituto de Ingenieros Eléctricos y Electrónicos) se encarga de la estandarización de tipos de datos y funciones más específicos para el diseño de hardware digital, abordando las complejidades del mundo real. Es aquí donde la robustez de los diseños VHDL toma una nueva dimensión.

Paquete std_logic_1164: Los Nueve Valores de la Lógica

El paquete std_logic_1164 es quizás el más utilizado y crucial de la biblioteca ieee. Su importancia radica en que define un sistema de lógica de nueve valores para los tipos de datos STD_ULOGIC (lógica de usuario no resuelta) y STD_LOGIC (lógica resuelta, que permite múltiples drivers en una señal). A diferencia del simple '0' y '1' del tipo BIT, estos nueve valores permiten modelar el comportamiento de las señales en circuitos digitales de una manera mucho más realista y detallada, capturando condiciones que ocurren en hardware físico, como estados desconocidos o alta impedancia.

Los nueve valores son:

'U'(Uninitialized): Indica que la señal no ha sido inicializada, un estado común al inicio de una simulación.'X'(Unknown): Representa un estado desconocido o contencioso, donde múltiples drivers intentan imponer valores conflictivos en una señal. Crucial para identificar errores de diseño.'0'(Logic 0): Lógica baja.'1'(Logic 1): Lógica alta.'Z'(High Impedance): Representa un estado de alta impedancia, donde una salida no está ni en '0' ni en '1', permitiendo que otra salida la controle (típico de buses tri-estado).'W'(Weak Unknown): Un estado débilmente desconocido, similar a 'X' pero con menor fuerza de conducción.'L'(Weak 0): Un '0' débil, que puede ser sobreescrito por un '0' o '1' fuerte.'H'(Weak 1): Un '1' débil, que puede ser sobreescrito por un '0' o '1' fuerte.'-'(Don't Care): Indica que el valor de la señal no importa en un contexto particular, útil para simplificar la lógica en ciertas condiciones o para especificar pruebas.

El uso de STD_LOGIC y STD_ULOGIC es vital para el diseño de circuitos complejos, ya que permiten la detección temprana de problemas como conflictos de bus, señales no inicializadas o condiciones indeterminadas, elementos críticos para asegurar la correcta fabricación y funcionamiento del chip. Esta granularidad en la descripción del estado de las señales contribuye enormemente a la interoperabilidad entre diferentes herramientas de diseño y entre distintos módulos creados por diferentes equipos.

La Sinergia entre Diseño y Simulación: Archivos VHDL y Test Benches

La utilidad de estas bibliotecas se manifiesta plenamente cuando se aplican en la estructura de un proyecto VHDL típico. Un proyecto generalmente consta de al menos dos tipos de archivos VHDL principales:

Archivo VHDL que contiene el dispositivo a simular (ej.

and2.vhd): Este archivo describe la lógica del circuito que deseamos implementar, como una compuerta AND de 2 entradas. Aquí es donde definimos las entidades (interfaces) y arquitecturas (comportamiento) de nuestros módulos de hardware. Dentro de este archivo, importamos las bibliotecas necesarias para definir los tipos de señales y las operaciones que utilizaremos. Por ejemplo, para usar el tipoSTD_LOGIC, tendríamos que incluir las siguientes líneas al principio del archivo:library ieee; use ieee.std_logic_1164.all;Estas líneas instruyen al compilador VHDL a buscar las definiciones de tipos y funciones en la biblioteca

ieeey, específicamente, en su paquetestd_logic_1164.

Archivo VHDL que contiene el dispositivo a simular (and2.vhd): En este caso una compuerta AND de 2 entrads. Archivo VHDL que contiene el test-bench de la and descripto anteriormente en otro archivo: (test_and2.vhd). Sección para la generación de las señales de estímulo. Archivo VHDL que contiene el test-bench (ej.

test_and2.vhd): Un test-bench es un módulo VHDL que no representa un hardware físico, sino un entorno de prueba para nuestro diseño. Su propósito es generar las señales de estímulo necesarias para probar el dispositivo bajo prueba (DUT - Device Under Test) y verificar que sus salidas se comporten según lo esperado. Aquí es donde el paquetetextiode la bibliotecastdcobra especial relevancia.La sección para la generación de las señales de estímulo dentro de un test-bench a menudo implica la creación de secuencias temporizadas de valores para las entradas del DUT. Por ejemplo, para una compuerta AND, podríamos aplicar la secuencia '00', '01', '10', '11' a sus entradas y observar la salida. Si esta secuencia es compleja o proviene de un archivo externo,

textioes indispensable para leer estos datos. Del mismo modo, los resultados de la simulación pueden ser escritos a un archivo usandotextiopara su posterior análisis o comparación con resultados esperados.La interacción entre el archivo de diseño y el test-bench, apoyada por las capacidades de las bibliotecas estándar, crea un ciclo de diseño y verificación robusto que es fundamental para el éxito en el desarrollo de hardware.

Comparativa de Bibliotecas Estándar en VHDL

Para resumir las diferencias y funciones principales de las bibliotecas std e ieee, la siguiente tabla ofrece una visión clara:

| Característica | Biblioteca std | Biblioteca ieee |

|---|---|---|

| Propósito Principal | Proveer los fundamentos del lenguaje VHDL, tipos de datos básicos y manejo de archivos. | Estandarizar tipos de datos para la descripción de hardware real y operaciones complejas. |

| Paquetes Clave Mencionados | standard, textio | std_logic_1164 |

| Tipos de Datos Asociados | BIT, BOOLEAN, INTEGER, REAL, TIME (en standard) | STD_ULOGIC, STD_LOGIC (en std_logic_1164) |

| Funcionalidad Destacada | Definición de tipos básicos y operaciones, lectura/escritura de archivos para simulación. | Modelado preciso de estados lógicos del hardware (9 valores), resolución de señales. |

| Importancia en el Diseño | Base del lenguaje, esencial para cualquier descripción. Facilita la automatización de pruebas. | Crucial para la robustez del diseño, detección de errores y interoperabilidad. |

Preguntas Frecuentes sobre las Bibliotecas Estándar de VHDL

¿Por qué son tan importantes las bibliotecas estándar en VHDL?

Las bibliotecas estándar son fundamentales porque proporcionan un conjunto predefinido y estandarizado de tipos de datos, funciones y procedimientos que son universalmente reconocidos por las herramientas VHDL. Esto asegura que los diseños sean portables, reusables y comprensibles por otros ingenieros. Sin ellas, cada diseñador tendría que definir sus propios tipos y operaciones básicas, lo que llevaría a la inconsistencia y dificultaría la colaboración y la verificación.

¿Es obligatorio usar std_logic_1164?

Aunque técnicamente no es "obligatorio" en el sentido de que VHDL permite otros tipos de datos (como BIT), el uso de STD_LOGIC y STD_ULOGIC definidos en el paquete std_logic_1164 es una práctica estándar y altamente recomendada en el diseño de hardware digital. Esto se debe a que los tipos de 9 valores permiten modelar con precisión las complejidades del hardware real (estados desconocidos, alta impedancia, etc.), lo cual es crucial para la simulación y síntesis de diseños robustos y para la detección temprana de problemas.

¿Para qué sirve textio en una simulación real?

En una simulación real, textio es indispensable para la automatización y la exhaustividad de las pruebas. Permite a los diseñadores leer secuencias de entrada (vectores de prueba) desde archivos externos, lo que facilita la aplicación de un gran número de escenarios de prueba sin tener que codificarlos manualmente en el test-bench. Además, permite registrar las salidas del diseño y otros datos relevantes en archivos, lo que es vital para la depuración, la comparación automática de resultados y la generación de informes de simulación, ahorrando tiempo y reduciendo errores humanos.

¿Qué sucede si no declaro una biblioteca o un paquete en mi archivo VHDL?

Si no declaras una biblioteca o un paquete utilizando las cláusulas library y use, el compilador VHDL no podrá encontrar las definiciones de los tipos de datos, funciones o componentes que provienen de esa biblioteca o paquete. Esto resultará en errores de compilación, ya que el compilador no reconocerá, por ejemplo, el tipo STD_LOGIC si no se ha importado ieee.std_logic_1164.all, o las funciones de manejo de archivos si no se ha importado std.textio.all.

En resumen, las bibliotecas estándar de VHDL son mucho más que una simple colección de herramientas; son el pilar que garantiza la eficiencia, la robustez y la estandarización en el diseño de hardware digital. Desde los tipos de datos más básicos hasta la modelización de estados complejos y la interacción con archivos externos, std e ieee proporcionan la infraestructura necesaria para transformar ideas en circuitos funcionales y confiables. Dominar su uso es un paso fundamental para cualquier ingeniero que aspire a crear diseños VHDL de alta calidad y listos para el mundo real.

Si quieres conocer otros artículos parecidos a El Corazón de VHDL: Bibliotecas Estándar y su Esencia puedes visitar la categoría Librerías.